Добро пожаловать на наш сайт !

Сигнальная цепь — это мост между реальным и цифровым миром. По мере увеличения частоты дискретизации АЦП и точности дискретизации скорость передачи сигнала интерфейсного чипа становится все выше и быстрее, и постепенно возникают различные проблемы высокоскоростной передачи сигнала. По сравнению с традиционной технологией передачи КМОП, внедрение LVDS или JESD204B в сигнальную цепь может обеспечить более высокую скорость передачи сигнала, более низкое энергопотребление, лучшую защиту от помех (лучшее соотношение сигнал/шум), а количество жгутов проводов будет значительно уменьшено. .

Что такое LVDS и JES204B?

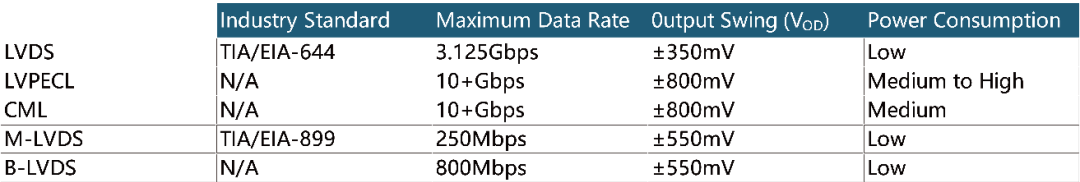

LVDS (Low-Voltage Differential Signaling) — это стандарт уровня для режима передачи сигналов, предложенный National Semiconductor (NS, теперь TI) в 1994 году. Он использует передачу с чрезвычайно низким колебательным напряжением. Высокоскоростные дифференциальные данные могут реализовываться как в двухточечном, так и в точечном режиме. Соединение с несколькими точками. Его преимущества заключаются в низком энергопотреблении, низком уровне битовых ошибок и низком уровне перекрестных помех. Он широко используется в различных случаях последовательной высокоскоростной передачи данных. Наиболее известными из них являются ноутбуки. ЖК-дисплей, высокоскоростная передача цифрового сигнала преобразователя данных (АЦП/ЦАП), передача видеопотока автомобильной электроники и т. д.

JESD204 — это высокоскоростной последовательный интерфейс, разработанный организацией по стандартизации JEDEC для передачи данных между преобразователями данных (АЦП и ЦАП) и логическими устройствами (FGPA). JESD204 использует технологию CML (Current-Mode Logic) для передачи сигналов. Версия B стандарта поддерживает скорость последовательной передачи данных до 12,5 Гбит/с и обеспечивает повторяемую детерминированную задержку для каналов JESD204. Поскольку скорость и разрешение преобразователей продолжают расти, а микросхемы FPGA все чаще поддерживают стандарт JESD204B, JESD204 становится все более распространенным в высокоскоростных преобразователях и интегрированных радиочастотных приемопередатчиках.

Практическое применение высокоскоростной передачи сигналов

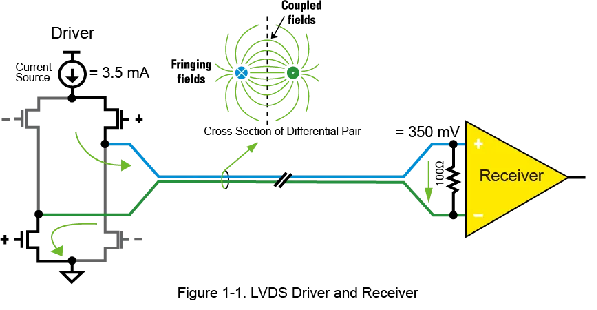

LVDS — это высокоскоростной сигнал, управляемый током, который применяет источник постоянного тока 3,5 мА на передающей стороне. Управляя включением и выключением переключающей трубки, ток, текущий от передающего конца к принимающему концу, может непрерывно меняться между прямым и обратным направлениями, тем самым достигая изменения дифференциального напряжения +/- 350 мВ на дифференциальной нагрузке 100 Ом на приемном устройстве. конец. Максимально может быть достигнута высокоскоростная передача данных 3,125 Гбит/с. LVDS использует дифференциальную линейную передачу, что дает несколько существенных преимуществ:

● a. Обеспечьте разность синфазных напряжений между передатчиком и приемником (в диапазоне 0–2,4 В).

● b Отличная помехоустойчивость и отличное соотношение сигнал/шум.

● c Чрезвычайно низкий размах напряжения и чрезвычайно низкое энергопотребление.

Рисунок 2. Как работает LVDS

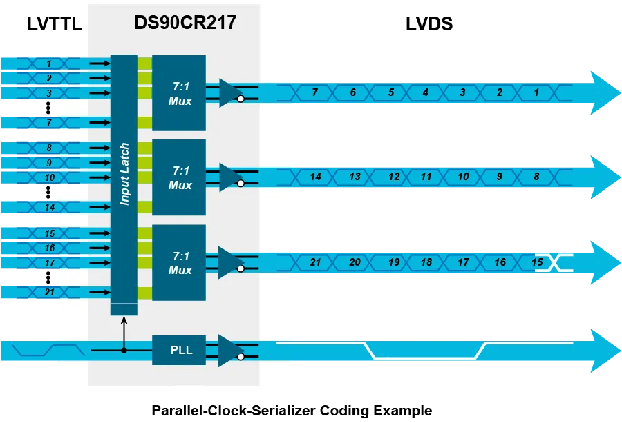

Традиционный LVDS использует метод синхронных часов, используя пару дифференциальных часов для обеспечения опорного сигнала для трех пар сигналов данных. В каждом такте каждая пара данных передает 7 бит информации. Чип SerDes необходим для преобразования параллельного сигнала в высокоскоростной последовательный сигнал посредством параллельного/последовательного преобразования при отправке; при получении высокоскоростного последовательного сигнала используйте последовательное/параллельное преобразование для восстановления параллельного сигнала.

Рисунок 3. Часы синхронизации LVDS предоставляют ссылку на данные.

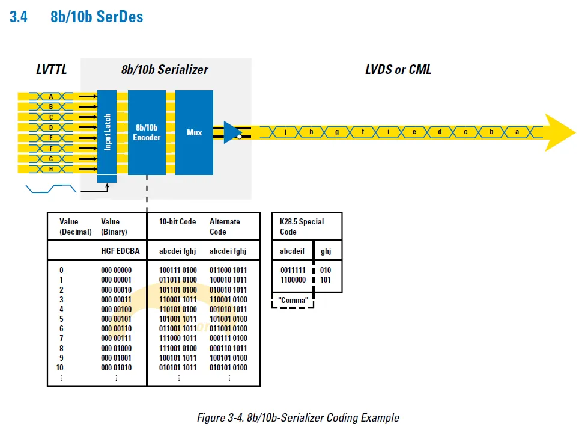

Используемый теперь LVDS также поддерживает 8b/10b SerDes для достижения более эффективной передачи сигнала. Этот метод передачи больше не требует использования тактового сигнала, а требует только передачи сигнала данных, сохраняя пару дифференциальных линий. Благодаря кодированию 8b/10b 8-битные действительные данные преобразуются в 10-битные закодированные данные. Хотя этот процесс увеличивает накладные расходы на 25%, он может гарантировать, что в данных будут достаточно частые переходы сигналов.

После получения сигнала тактовый сигнал восстанавливается из данных посредством системы фазовой автоподстройки частоты (ФАПЧ). Такая архитектура передачи называется встроенными часами (Embeded Clock). Кодирование 8b/10b также может обеспечить баланс постоянного тока для передаваемого сигнала, то есть количество единиц и количество нулей в основном поддерживаются равными. Сбалансированные линии передачи постоянного тока могут быть соединены последовательно с блокирующими конденсаторами постоянного тока для улучшения характеристик шума и джиттера в линии. Встроенные часы и 8b/10b широко используются в промышленных стандартах высокоскоростной передачи, таких как PCIe, SATA, USB3 и т. д., включая JESD204 (CML).

Рисунок 4. Как работают встроенные часы LVDS (источник изображения TI)

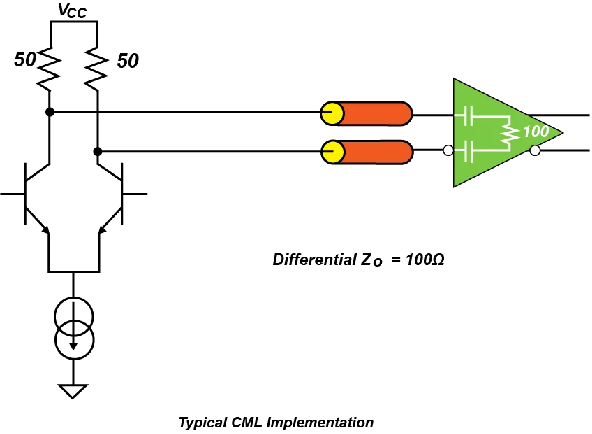

В отличие от LVDS, CML (логика текущего режима) использует метод управления напряжением для подачи постоянного напряжения Vcc на стороне источника. Управляя включением и выключением переключающей трубки, принимающая сторона может получать изменяющееся дифференциальное напряжение. CML использует встроенную тактовую частоту и кодирование 8b/10b с более высоким рабочим напряжением, чем LVDS. Он также использует технологию выравнивания в передающих и принимающих микросхемах, чтобы обеспечить превосходный уровень ошибок по битам во время высокоскоростной передачи на большие расстояния. JESD204B, использующий технологию CML, может поддерживать скорость передачи данных до 12,5 Гбит/с, а его последняя версия C может даже поддерживать скорость передачи данных до 32 Гбит/с.

Рисунок 5. Способ передачи сигнала CML

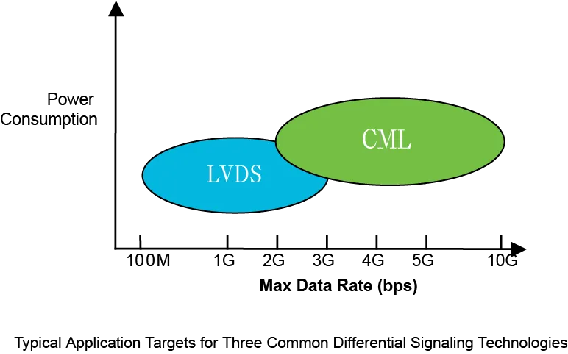

Итак, когда мы проектируем микросхемы высокоскоростного интерфейса, следует ли нам использовать LVDS или CML (JESD204)? Простой принцип заключается в том, что CML имеет более высокую скорость, а LVDS потребляет меньше энергии.

Рисунок 6. Выбор LVDS и CML

Когда скорость передачи данных ниже 2 Гбит/с, более широко используется LVDS с более низким энергопотреблением, сильной защитой от помех и широким диапазоном синфазного напряжения, что делает требования к межсоединению очень низкими. LVDS также имеет стандарты M-LVDS и B-LVDS, которые поддерживают многоточечное соединение, которое может соединять несколько узлов и иметь множество сценариев применения. Если скорость передачи данных превышает 3,125 Гбит/с, необходимо использовать CML. Когда скорость передачи данных находится в диапазоне от 2G до 3,125 Гбит/с, необходимо комплексно учитывать баланс функциональности, производительности и энергопотребления. Например, если расстояние передачи велико, но требования к качеству сигнала очень высоки, рассмотрите возможность использования CML; когда расстояние передачи короткое и требуется длительное время автономной работы и низкое энергопотребление, рассмотрите возможность использования LVDS;